DTMF Radio Receiver

DTMF Radio Receiver The complete background about this project can be found at my "Wife replace" project.

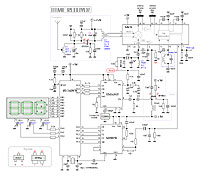

This part is a FM receiver based on a PLL synthesizer UMA1015.

The complete background about this project can be found at my "Wife replace" project.

This part is a FM receiver based on a PLL synthesizer UMA1015.  Preamplifier:

Preamplifier: In the SA615 you will find an oscillator at pin 3 and 4. This oscillator is connected internally

to mixer 1.

In the SA615 you will find an oscillator at pin 3 and 4. This oscillator is connected internally

to mixer 1. |

|

| repeat_rec.zip | DTMF Radio Receiver program (the hex file is zipped!). |

| plls.zip | Basic function of PLL (the doc file is zipped!). |

Final word

Final word